PCIe高速总线技术趋势及测试解决方案(上)

在计算机硬件的复杂体系中,PCIe高速总线技术作为一个关键要素,为系统的高效运行提供着有力支撑。在计算机组装过程中,您可能留意到主板上长短各异的插槽;在关注显卡性能时,或许也听闻过PCIe通道对其性能发挥的重要作用。那么,PCIe究竟是什么?它又是如何对我们的数字生活产生深远影响的呢?本文将深入探讨PCIe,解析其技术内涵与应用价值。

一、技术起源与发展历程及原理

PCIe全称Peripheral Component Interconnect Express,是高速串行计算机扩展总线标准,它的出现,可谓是计算机总线发展史上的重大变革。在PCIe诞生前,并行总线PCI占据主导,但随着计算机硬件性能发展,其在信号干扰、带宽扩展等方面的局限性日益凸显。

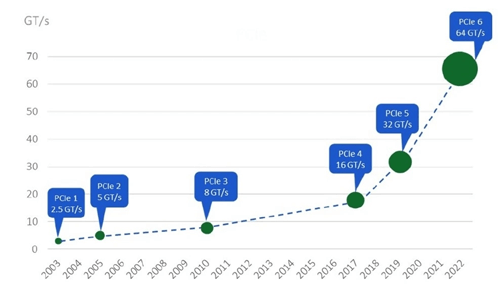

2003 年,PCIe 1.0 版本问世,开启串行互联新时代。它采用点对点串行通信,减少信号干扰,提升数据传输效率,单通道传输速率2.5GT/s ,采用8b/10b编码。此后PCIe不断升级,2007 年的PCIe 2.0速率翻倍至5GT/s,2010年PCIe 3.0速率提升到8GT/s,引入128b/130b 编码,降低编码开销,提升有效带宽。2017年PCIe 4.0速率达 16GT/s ,2019 年 PCIe 5.0达32GT/s,2022年PCIe 6.0飞跃至64GT/s ,每次版本更迭都让数据传输更高效。

PCIe其核心技术原理包含以下方面:

二、PCIe高速总线技术的应用场景

PCIe高速总线技术凭借其卓越的性能,在众多领域都有着广泛而深入的应用,成为推动各行业技术发展的关键力量。

(1)数据中心与云计算。

云计算发展使数据中心对计算和存储资源需求大增,PCIe技术支撑其高效运行。它支持GPU资源池化,多台服务器通过PCIe交换机共享GPU资源,提升利用率、降低成本。在分布式存储方面,Ceph集群利用PCIe NVMe – oF(NVMe over Fabrics)扩展存储池,提升存储系统性能与扩展性,为云计算提供强大存储支持。

(2)人工智能与深度学习

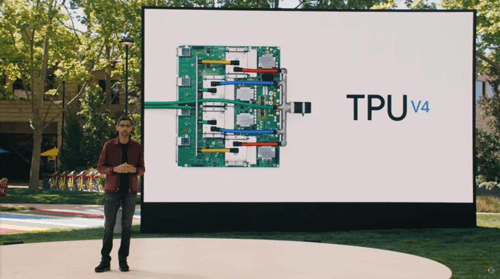

人工智能与深度学习对数据传输带宽和延迟要求高,PCIe高速总线技术可以满足需求。在AI训练集群,如谷歌TPU v4通过PCIe 4.0互联构建超算集群,提升训练效率;边缘推理设备Jetson AGX Xavier通过PCIe连接多传感器实现实时物体识别,助力智能应用。

(3)消费电子

在消费电子领域,PCIe带来更好使用体验。外置显卡坞通过PCIe Thunderbolt 3接口外接桌面显卡,提升笔记本图形处理能力;雷电4接口基于PCIe 3.0 x4,支持外接SSD或8K显示器,加快读写速度、带来震撼视觉体验。

(4)医疗成像与科研设备

在医疗成像和科研设备领域,PCIe高速总线技术作用关键。GE Revolution CT通过PCIe 3.0 x16传输3D断层扫描数据,方便医生及时诊断;CERN LHC实验设备通过PCIe 4.0 x8采集粒子碰撞数据,助力科研人员探索微观世界。

三、PCIe高速总线技术的发展趋势

PCIe高速互连核心技术的发展,为计算机硬件的性能提升带来了巨大的推动作用。它们以更高的传输速率、更强大的带宽能力以及更先进的技术特性,为满足算力需求迭代在数据中心、高性能计算、AI等众多场景发挥着关键作用,成为推动这些领域发展的重要力量,同时向更高速率和多协议融合演进。

(1)速率持续提升

PCIe发展中速率提升是关键。2022年发布的PCIe 6.0速率达64GT/s,翻倍于PCIe 5.0,采用PAM4技术但带来信号完整性挑战,引入轻量级FEC技术降低误码率,在相同时钟频率下实现两倍数据速率,x16通道带宽可达256GB/s,能满足AI大模型训练中 GPU、加速器间海量数据传输需求,且行业预测该版本现在进入了加速落地阶段。目前PCIe 7.0在研发,目标速率128GT/s,以满足超大规模数据中心和高性能计算等领域对高速数据传输需求。

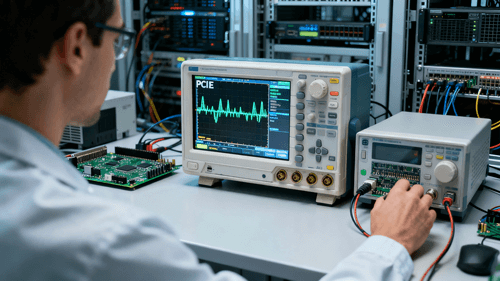

不管是5.0还是6.0亦或是未来的7.0,速度越快,越容易出现信号不稳定、数据丢包等问题。就像高速公路需要定期检修,PCIe设备也需要严格的测试,才能保证出厂后稳定运行。

由此而生了PCIe协议分析仪和相关测试解决方案,其测试方案是围绕高速率带来的信号完整性等问题,形成了覆盖物理层等多维度的专业化、自动化解决方案,以应对PCIe技术发展带来的挑战。毕竟更加智能化、自动化的测试工具将有助于提高测试效率和准确性,保障PCIe设备的性能和兼容性。

(2)应用场景多元化

PCIe应用场景不断拓展。AI领域,其高带宽为GPU、TPU等AI加速器的大规模并行计算提供支持;数据中心中,NVMe SSD存储设备通过PCIe接口实现超低延迟存储访问;PCIe作为多高速协议的基础底座,与CXL(Compute Express Link)专属协议融合深度绑定,打破传统PCIe架构内存共享和设备互连瓶颈,大幅提升计算密集型任务的处理效率;边缘计算与物联网领域,PCIe向小型化、低功耗方向演进,满足车载系统等实时数据处理需求。

(3)技术优化与生态协同

技术优化上,PCIe 6.0精简协议层与改进流量控制机制降低传输延迟,能效提升技术适配移动设备等节能需求,还推动新型存储形态发展。生态协同方面,PCIe新版本保持向后兼容性,保障企业设备升级平滑过渡,且积极与新兴标准协同构建异构计算生态。同时,为解决高速率下的链路损耗问题,Retimer等辅助芯片成为关键配套技术。这类芯片能补偿信号衰减、优化信号完整性,助力PCIe 6.0等高速版本在复杂硬件环境中稳定部署。

未来,PCIe技术将继续在速率提升、应用拓展和技术优化等方面持续创新。随着人工智能、云计算、物联网等新兴技术的迅猛发展,其应用场景也将进一步多元化,不仅在传统的计算机领域,还将在汽车电子、工业自动化、医疗设备等更多领域发挥重要作用。